SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# BICMOS PFC/PWM COMBINATION CONTROLLER

## **FEATURES**

- Combines PFC and Downstream Converter Controls

- Controls Boost Preregulator to Near-Unity Power Factor

- Accurate Power Limiting

- Improved Feedforward Line Regulation

- Peak Current-Mode Control in Second Stage

- Programmable Oscillator

- Leading-Edge/Trailing-Edge Modulation for Reduced Output Ripple

- Low Start-up Supply Current

- Synchronized Second Stage Start-Up, with Programmable Soft-start

- Programmable Second Stage Shutdown

## DESCRIPTION

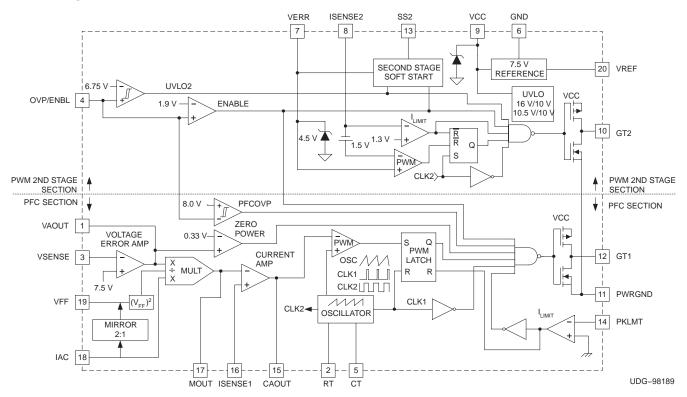

The UCC2850x family provides all of the control functions necessary for an active power-factor-corrected preregulator and a second-stage dc-to- dc converter. The controller achieves near-unity power factor by shaping the ac input line current waveform to correspond to the ac input-line voltage using average current-mode control. The dc-to-dc converter uses peak current-mode control to perform the step-down power conversion.

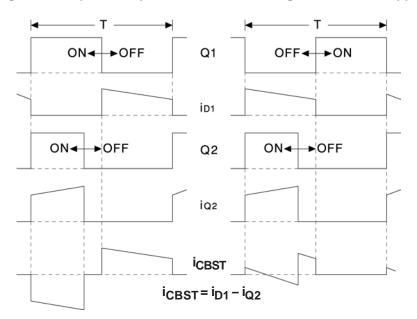

The PFC stage is leading-edge modulated while the second stage is trailing-edge synchronized to allow for minimum overlap between the boost and PWM switches. This reduces ripple current in the bulk-output capacitor.In order to operate with over three-to-one range of input-line voltages, a line feedforward ( $V_{FF}$ ) is

used to keep input power constant with varying input voltage. Generation of V<sub>FF</sub> is accomplished using  $I_{AC}$  in conjunction with an external single-pole filter. This not only reduces external parts count, but also avoids the use of high-voltage components, offering a lower-cost solution. The multiplier then divides the line current by the square of V<sub>FF</sub>.

The UCC2850x PFC section incorporates a low offset-voltage amplifier with 7.5-V reference, a highly-linear multiplier capable of a wide current range, a high-bandwidth, low offset-current amplifier, with a noise-attenuation configuration, novel PWM comparator and latch, and a high-current output driver. Additional PFC features include over-voltage protection, zero-power detection to turn off the output when VAOUT is below 0.33 V and peak current and power limiting.

The dc-to-dc section relies on an error signal generated on the secondary-side and processes it by performing peak current mode control. The dc-to-dc section also features current limiting, a controlled soft-start, preset operating range with selectable options, and 50% maximum duty cycle.

The UCC28500 and UCC28502 have a wide UVLO threshold (16.5 V/10 V) for bootstrap bias supply operation. The UCC28501 and UCC28503 are designed with a narrow UVLO range (10.5 V/10 V) more suitable for fixed bias operation. The UCC28500 and UCC28501 have a narrow UVLO threshold for PWM stage (to allow operation down to 75% of nominal bulk voltage), while the UCC28502 and UCC38503 are configured for a much wider operation range for the PWM stage (down to 50% of bulk nominal voltage).

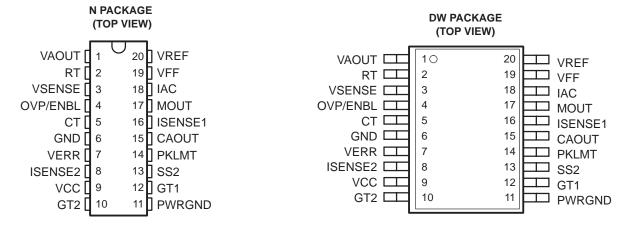

Available in 20-pin N and DW packages.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

| absolute maximum ratings over operating free-air temperature (unless oth Supply Voltage VCC | •              |

|---------------------------------------------------------------------------------------------|----------------|

| Gate Drive Current                                                                          |                |

| Continuous                                                                                  | 0.2 A          |

| Pulsed                                                                                      | 1.2 A          |

| Input Voltage                                                                               |                |

| ISENSE1, ISENSE2, MOUT, VSENSE, OVP/ENBL                                                    |                |

| CAI, MOUT, CT                                                                               | 8 V            |

| PKLMT, VERR                                                                                 | 5 V            |

| Input Current                                                                               |                |

| RSET, RT, IAC, PKLMT, ENA                                                                   | 10 mA          |

| VCC (no switching)                                                                          |                |

| Maximum Negative Voltage GT1, GT2, PKLMT, MOUT                                              | –0.5 V         |

| Power Dissipation                                                                           | 1 W            |

| Storage temperature T <sub>stg</sub>                                                        | –65°C to 150°C |

| Junction temperature T <sub>J</sub>                                                         | –55°C to 125°C |

| Lead temperature (soldering, 10 sec)                                                        | 300°C          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup>Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages. All voltages are referenced to GND.

|               | PFC THR                       | ESHOLD                     | PACKAGED DEVICES   |                       |  |

|---------------|-------------------------------|----------------------------|--------------------|-----------------------|--|

| Тյ            | UVLO TURN-ON<br>THRESHOLD (V) | UVLO2<br>HYSTERESIS<br>(V) | PLASTIC DIP<br>(N) | SMALL OUTLINE<br>(DW) |  |

|               | 16                            | 1.2                        | UCC28500N          | UCC28500DW            |  |

| –40°C to 85°C | 10.5                          | 1.2                        | UCC28501N          | UCC28501DW            |  |

| -40°C 10 85°C | 16                            | 3.0                        | UCC28502N          | UCC28502DW            |  |

|               | 10.5                          | 3.0                        | UCC28503N          | UCC28503DW            |  |

|               | 16                            | 1.2                        | UCC38500N          | UCC38500DW            |  |

| 0°C to 70°C   | 10.5                          | 1.2                        | UCC38501N          | UCC38501DW            |  |

| 0000700       | 16                            | 3.0                        | UCC38502N          | UCC38502DW            |  |

|               | 10.5                          | 3.0                        | UCC38503N          | UCC38503DW            |  |

#### AVAILABLE OPTIONS

The DW package is available taped and reeled. Add TR suffix to device type (e.g. UCC38500DWTR) to order quantities of 2000 devices per reel.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# electrical characteristics $T_A = 0^{\circ}C$ to $70^{\circ}C$ for the UCC3850X, -40°C to 85°C for the UCC2850X, $T_A = T_J$ , VCC = 12 V, RT = 22 k $\Omega$ , CT = 330 pF (unless otherwise noted)

#### supply current

| PARAMETER           | TEST CONDITIONS                    | MIN | TYP | MAX | UNITS |

|---------------------|------------------------------------|-----|-----|-----|-------|

| Supply current, off | VCC turn-on threshold –300 mV      |     | 150 | 300 | μA    |

| Supply current, on  | VCC = 12 V (no load on GT1 or GT2) |     | 4   | 6   | mA    |

#### undervoltage lockout

| PARAMETER                            | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-----------------|------|------|------|-------|

| VCC turn-on threshold (UCCx8500/502) |                 | 15.4 | 16   | 16.6 | V     |

| UVLO hysteresis (UCCx8500/502)       |                 | 5.8  | 6.3  |      | V     |

| Shunt voltage (UCCx8500/502)         | IVCC = 10 mA    | 15.4 | 16.2 | 17.0 | V     |

| VCC turn-on threshold (UCCx8501/503) |                 | 9.7  | 10.2 | 10.8 | V     |

| VCC turn-off threshold               |                 | 9.4  | 9.7  |      | V     |

| UVLO hysteresis (UCCx8501/503)       |                 | 0.3  | 0.5  |      | V     |

#### voltage amplifier

| PARAMETER                 | TEST CONDITIONS                        | MIN   | ТҮР   | MAX   | UNITS |

|---------------------------|----------------------------------------|-------|-------|-------|-------|

|                           | $0^{\circ}C \le T_{A} \le 70^{\circ}C$ | 7.387 | 7.500 | 7.613 | V     |

| Input voltage             | $-40^{\circ}C \le T_A \le 85^{\circ}C$ | 7.35  | 7.50  | 7.65  | V     |

| VSENSE bias current       |                                        |       | 50    | 200   | nA    |

| Open loop gain            | VAOUT = 2 V to 5 V                     | 50    | 90    |       | dB    |

| High-level output voltage | $I_{LOAD} = -150 \ \mu A$              | 5.3   | 5.5   | 5.6   | V     |

| Low-level output voltage  | I <sub>LOAD</sub> = 150 μA             | 0.00  | 0.05  | 0.15  | V     |

#### PFC overvoltage protection and enable

| PARAMETER              | TEST CONDITIONS | MIN             | ТҮР             | MAX             | UNITS |

|------------------------|-----------------|-----------------|-----------------|-----------------|-------|

| Over voltage reference |                 | VREF<br>+ 0.480 | VREF<br>+ 0.500 | VREF<br>+ 0.520 | V     |

| Hysteresis             |                 | 300             | 500             | 600             | mV    |

| Enable threshold       |                 | 1.7             | 1.9             | 2.1             | V     |

| Enable hysteresis      |                 | 0.1             | 0.2             | 0.3             | V     |

#### current amplifier

| PARAMETER                   | TEST CONDITIONS                            | MIN | TYP | MAX  | UNITS |

|-----------------------------|--------------------------------------------|-----|-----|------|-------|

| Input offset voltage        | $V_{CM} = 0 V$ , $V_{CAOUT} = 3 V$         | -6  | 0   | 6    | mV    |

| Input bias current          | $V_{CM} = 0 V$ , $V_{CAOUT} = 3 V$         |     | -50 | -100 | nA    |

| Input offset current        | $V_{CM} = 0 V$ , $V_{CAOUT} = 3 V$         |     | 25  | 100  | nA    |

| Open loop gain              | $V_{CM} = 0 V$ , $V_{CAOUT} = 2 V to 5 V$  | 90  |     |      | dB    |

| Common-mode rejection ratio | $V_{CM} = 0 V$ to 1.5 V, $V_{CAOUT} = 3 V$ | 90  |     |      | dB    |

| High-level output voltage   | $I_{LOAD} = -120 \ \mu A$                  | 5.6 | 7.0 | 7.5  | V     |

| Low-level output voltage    | I <sub>LOAD</sub> = 1 mA                   | 0.1 | 0.2 | 0.5  | V     |

| Gain bandwidth product      | See Note 1                                 |     | 2.5 |      | MHz   |

NOTES: 1. Ensured by design. Not production tested.

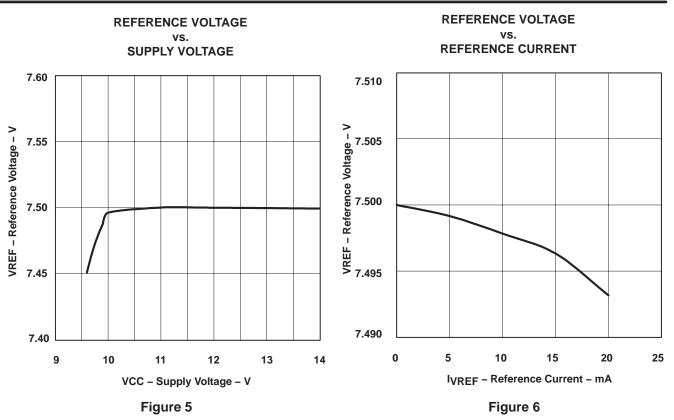

2. See Figure 6 for reference variation.

3. See Figure 5 for reference variation for VCC < 10.8 V.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# electrical characteristics $T_A = 0^{\circ}C$ to $70^{\circ}C$ for the UCC3850X, -40°C to 85°C for the UCC2850X, $T_A = T_J$ , VCC = 12 V, RT = 22 k $\Omega$ , CT = 330 pF (unless otherwise noted)

#### voltage reference

| PARAMETER             | TEST CONDITIONS                              | MIN   | TYP   | MAX   | UNITS |

|-----------------------|----------------------------------------------|-------|-------|-------|-------|

| land only and         | $T_A = 0^{\circ}C$ to $70^{\circ}C$          | 7.387 | 7.500 | 7.613 | V     |

| Input voltage         | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$ | 7.35  | 7.50  | 7.65  | V     |

| Load regulation       | IREF = -1 mA to -2 mA, See Note 2            | 0     |       | 10    | mV    |

| Line regulation       | VCC = 10.8 V to 15 V, See Note 3             | 0     |       | 10    | mV    |

| Short circuit current | VREF = 0V                                    | -20   | -25   | -50   | mA    |

#### oscillator

| PARAMETER                             | TEST CONDITIONS      | MIN | TYP | MAX | UNITS |

|---------------------------------------|----------------------|-----|-----|-----|-------|

| Frequency, initial accuracy           | $T_A = 25^{\circ}C$  | 85  | 100 | 115 | kHz   |

| Frequency, voltage stability          | VCC = 10.8 V to 15 V | -1% |     | 1%  |       |

| Frequency, total variation            | Line, Temp           | 80  |     | 120 | kHz   |

| Ramp peak voltage                     |                      | 4.5 | 5   | 5.5 | V     |

| Ramp amplitude voltage (peak to peak) |                      | 3.5 | 4   | 4.5 | V     |

#### peak current limit

| PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------|-----------------|-----|-----|-----|-------|

| PKLMT reference voltage |                 | -15 | 0   | 15  | mV    |

| PKLMT propagation delay |                 | 150 | 300 | 500 | ns    |

#### multiplier

| PARAMETER                                  | TEST CONDITIONS                                                                                                                                                                                                   | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| IMOUT, high-line low-power output current  | $\begin{split} I_{AC} = 500 \; \mu\text{A}, \; \text{VFF} = 4.7 \; \text{V},  \text{VAOUT} = 1.25 \; \text{V}, \\ 0^\circ\text{C} \leq \text{T}_A \leq 85^\circ\text{C} \end{split}$                              | 0    | -6   | -20  |       |

| IMOUT, high-line low-power output current  | $\label{eq:IAC} \begin{array}{ll} I_{AC} = 500 \; \mu \text{A}, \; \text{VFF} = 4.7 \; \text{V}, & \text{VAOUT} = 1.25 \; \text{V}, \\ -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C} \end{array}$ | 0    | -6   | -23  |       |

| IMOUT, high-line high-power output current | $I_{AC} = 500 \ \mu\text{A}, \ \text{VFF} = 4.7 \ \text{V},  \text{VAOUT} = 5 \ \text{V}$                                                                                                                         | -70  | -90  | -105 | μA    |

| IMOUT, low-line low-power output current   | $I_{AC} = 150 \ \mu A, \ VFF = 1.4 \ V, \ VAOUT = 1.25 \ V$                                                                                                                                                       | -10  | -19  | -50  |       |

| IMOUT, low-line high-power output current  | $I_{AC} = 150 \ \mu\text{A}, \ \text{VFF} = 1.4 \ \text{V},  \text{VAOUT} = 5 \ \text{V}$                                                                                                                         | -268 | -300 | -345 |       |

| IMOUT, IAC-limited output current          | $I_{AC} = 150 \ \mu\text{A}, \ \text{VFF} = 1.3 \ \text{V},  \text{VAOUT} = 5 \ \text{V}$                                                                                                                         | -250 | -300 | -400 |       |

| Gain constant (K)                          | $I_{AC} = 300 \ \mu\text{A}, \ \text{VFF} = 2.8 \ \text{V},  \text{VAOUT} = 2.5 \ \text{V}$                                                                                                                       | 0.5  | 1    | 1.5  |       |

|                                            | $I_{AC} = 150 \ \mu A, \ VFF = 1.4 \ V, \ VAOUT = 0.25 \ V$                                                                                                                                                       |      | 0    | -2   | 1/V   |

|                                            | $I_{AC} = 500 \ \mu A, \ VFF = 4.7 \ V, \ VAOUT = 0.25 \ V$                                                                                                                                                       |      | 0    | -2   | μA    |

| IMOUT, zero current                        | $\label{eq:IAC} \begin{array}{ll} I_{AC} = 500 \; \mu \text{A}, \; \text{VFF} = 4.7 \; \text{V}, & \text{VAOUT} = 0.5 \; \text{V}, \\ 0^\circ \text{C} \leq \text{T}_A \leq 85^\circ \text{C} \end{array}$        |      | 0    | -3   | μΑ    |

|                                            | $\label{eq:IAC} \begin{array}{ll} I_{AC} = 500 \; \mu \text{A}, \; \text{VFF} = 4.7 \; \text{V}, & \text{VAOUT} = 0.5 \; \text{V}, \\ -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C} \end{array}$  |      | 0    | -3.5 | μΑ    |

| Power limit ( $I_{MOUT} \times V_{FF}$ )   | I <sub>AC</sub> = 150 μA, VFF = 1.4 V, VAOUT = 5 V                                                                                                                                                                | -375 | -420 | -485 | μW    |

#### zero power

| PARAMETER                       | TEST CONDITIONS   | MIN   | TYP   | MAX   | UNITS |

|---------------------------------|-------------------|-------|-------|-------|-------|

| Zero power comparator threshold | Measured on VAOUT | 0.175 | 0.330 | 0.500 | V     |

NOTES: 1. Ensured by design. Not production tested.

2. See Figure 6 for reference variation.

3. See Figure 5 for reference variation for VCC < 10.8 V .

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# electrical characteristics $T_A = 0^{\circ}C$ to $70^{\circ}C$ for the UCC3850X, $-40^{\circ}C$ to $85^{\circ}C$ for the UCC2850X, $T_A = T_J$ , VCC = 12 V, RT = 22 k $\Omega$ , CT = 330 pF (unless otherwise noted)

#### **PFC** gate driver

| PARAMETER                     | TEST CONDITIONS                                                                                                                        | MIN | TYP | MAX  | UNITS |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| GT1 pull up resistance        | IOUT from -100 mA to -200 mA                                                                                                           |     | 5   | 12   | Ω     |

| GT1 pull down resistance      | I <sub>OUT</sub> = 100 mA                                                                                                              |     | 2   | 10   | Ω     |

| GT1 output rise time          | $\begin{array}{ll} C_{LOAD} = 1 \text{ nF}, & R_{LOAD} = 10 \ \Omega \\ V_{GT1} \text{ from } 0.7 \ V \text{ to } 9.0 \ V \end{array}$ |     | 25  | 50   | ns    |

| GT1 output fall time          | $\begin{array}{ll} C_{LOAD} = 1 \text{ nF}, & R_{LOAD} = 10 \ \Omega \\ V_{GT1} \text{ from } 9.0 \ V \text{ to } 0.7 \ V \end{array}$ |     | 10  | 50   | ns    |

| Maximum duty cycle            |                                                                                                                                        | 93% | 95% | 100% |       |

| Minimum controlled duty cycle | f = 100 kHZ                                                                                                                            |     |     | 2%   |       |

#### second stage undervoltage lockout (UVLO2)

| PARAMETER                            | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-----------------|------|------|------|-------|

| PWM turn-on reference (UCCx8500/501) |                 | 6.30 | 6.75 | 7.30 | V     |

| Hysteresis (UCCx8500/501)            |                 | 0.96 | 1.20 | 1.44 | V     |

| PWM turn-on reference (UCCx8502/503) |                 | 6.30 | 6.75 | 7.30 | V     |

| Hysteresis (UCCx8502/503)            |                 | 2.4  | 3    | 3.6  | V     |

#### second stage soft-start

| PARAMETER             | TEST CONDITIONS                      | MIN  | TYP | MAX   | UNITS |

|-----------------------|--------------------------------------|------|-----|-------|-------|

| SS2 charge current    |                                      | -7.3 | -10 | -12.5 | μΑ    |

| Input voltage (VERR)  | I <sub>VERR</sub> = 2 mA,UVLO = Low  |      |     | 300   | mV    |

| SS2 discharge current | ENBL = High, UVLO = Low, SS2 = 2.5 V | 3    |     | 10    | mA    |

#### second stage duty cycle clamp

| PARAMETER          | MIN | ТҮР | MAX | UNITS |  |

|--------------------|-----|-----|-----|-------|--|

| Maximum duty cycle |     | 44% |     | 50%   |  |

#### second stage pulse-by-pulse current sense

| PARAMETER                          | PARAMETER TEST CONDITIONS        |      | TYP  | MAX  | UNITS |

|------------------------------------|----------------------------------|------|------|------|-------|

| Current sense comparator threshold | VERR = 2.5 V measured on ISENSE2 | 0.94 | 1.05 | 1.15 | V     |

#### second stage overcurrent limit

| PARAMETER                         | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|-----------------|------|------|------|-------|

| Peak current comparator threshold |                 | 1.15 | 1.30 | 1.45 | V     |

| Input bias current                |                 |      | 50   |      | nA    |

#### second stage gate driver

| PARAMETER                | TEST CONDITIONS                                                                        | MIN | TYP | MAX | UNITS |

|--------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|-------|

| GT2 pull up resistance   | IOUT from –100 mA to –200 mA                                                           |     | 5   | 12  | Ω     |

| GT2 pull down resistance | I <sub>OUT</sub> = 100 mA                                                              |     | 3   | 10  | Ω     |

| GT2 output rise time     | $C_{LOAD} = 1 \text{ nF,R}_{LOAD} = 10 \Omega$<br>V <sub>GT2</sub> from 0.7 V to 9.0 V |     | 25  | 50  | ns    |

| GT2 output fall time     | $C_{LOAD} = 1 \text{ nF,R}_{LOAD} = 10 \Omega$<br>V <sub>GT2</sub> from 9.0 V to 0.7 V |     | 25  | 50  | ns    |

NOTES: 1. Ensured by design. Not production tested.

2. See Figure 6 for reference variation.

3. See Figure 5 for reference variation for VCC < 10.8 V .

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## pin assignments

**CAOUT:** (current amplifier output) This is the output of a wide bandwidth operational amplifier that senses line current and commands the PFC pulse width modulator (PWM) to force the correct duty cycle. This output can swing close to GND, allowing the PWM to force zero duty cycle when necessary.

CT: (oscillator timing capacitor) A capacitor from CT to GND sets the oscillator frequency according to:

$$f = \frac{0.725}{\left(R_{T} \times C_{T}\right)}$$

**GND:** (ground) All voltages measured with respect to ground. VCC and VREF should be bypassed directly to GND with a 0.1- $\mu$ F or larger ceramic capacitor. The timing capacitor discharge current also returns to this pin, so the lead from the oscillator timing capacitor to GND should be as short and direct as possible.

**GT1:** (gate drive) The output drive for the PFC stage is a totem pole MOSFET gate driver on GT1. Use a series gate resistor of at least 10.5  $\Omega$  to prevent interaction between the gate impedance and the GT1 output driver that might cause the GT1 to overshoot excessively. Some overshoot of the GT1 output is always expected when driving a capacitive load. Refer to Figure 4 for gate drive resistor selections.

GT2: (gate drive) Same as output GT1 for the second stage output drive. Limited to 50% maximum duty cycle.

**IAC:** (input ac current) This input to the analog multiplier is a current. The multiplier is tailored for very low distortion from this current input ( $I_{AC}$ ) to MOUT, so this is the only multiplier input which should be used for sensing instantaneous line voltage. Recommended maximum  $I_{AC}$  is 500  $\mu$ A.

**ISENSE1:** (current sense) This is the non-inverting input to the current amplifier. This input and the inverting input MOUT remain functional down to and below GND.

**ISENSE2:** (current sense) A resistor from the source of the lower FET to ground generates the input signal for the peak limit control of the second stage. The oscillator ramp can also be summed into this pin, for slope compensation.

**MOUT:** (multiplier output and current sense amplifier inverting input) The output of the analog multiplier and the inverting input of the current amplifier are connected together at MOUT. As the multiplier output is a current, this is a high impedance input so the amplifier can be configured as a differential amplifier to reject ground noise. Multiplier output current is given by:

$$I_{MOUT} = \frac{\left(V_{VAOUT} - 1.0\right) \times I_{IAC}}{\kappa \times \left(V_{VFF}\right)^2}$$

Connect current loop compensation components between MOUT and CAOUT.

**OVP/ENBL:** (over-voltage/enable) A window comparator input which disables the PFC output driver if the boost output is 6.67% above nominal or disables both the PFC and second stage output drivers and reset SS2 if pulled below 1.9 V. This input is also used to determine the active range of the second stage PWM.

**PKLMT:** (PFC peak current limit) The threshold for peak limit is 0 V. Use a resistor divider from the negative side of the current sense resistor to VREF to level-shift this signal to a voltage corresponding to the desired overcurrent threshold across the current sense resistor.

**PWRGND:** Ground for totem pole output drivers.

**RT:** (oscillator charging current) A resistor from RT to GND is used to program oscillator charging current. A resistor between 10 k $\Omega$  and 100 k $\Omega$  is recommended. Nominal voltage on this pin is 3 V.

## pin assignments (continued)

**SS2:** (soft-start for PWM) SS2 is at ground for either enable low or OVP/ENBL below the UVLO2 threshold conditions. When enabled, SS2 charges an external capacitor with a current source. This voltage is used as the voltage error signal during start-up, enabling the PWM duty cycle to increase slowly. In the event of a disable command or a UVLO2 dropout, SS2 quickly discharges to disable the PWM.

**VAOUT:** (voltage amplifier output) This is the output of the operational amplifier that regulates output voltage. The voltage amplifier output is internally limited to approximately 5.5 V to prevent overshoot.

**VCC:** (positive supply voltage) Connect to a stable source of at least 20 mA between 12 V and 17 V for normal operation. Bypass VCC directly to GND to absorb supply current spikes required to charge external MOSFET gate capacitances. To prevent inadequate gate drive signals, the output devices are inhibited unless VCC exceeds the upper under-voltage lockout threshold and remains above the lower threshold.

**VERR:** (voltage amp error signal for the second stage) The error signal is generated by an external amplifier which drives this pin. This pin has an internal 4.5-V voltage clamp that limits GT2 to less than 50% duty cycle to ensure transformer reset in the typical application.

**VFF:** (RMS feed forward signal) VFF signal is generated at this pin by mirroring one-half of I<sub>AC</sub> into a single pole external filter. At low line, the VFF voltage should be 1.4 V.

**VSENSE:** (voltage amplifier inverting input) This is normally connected to a compensation network and to the boost converter output through a divider network.

**VREF:** (voltage reference output) VREF is the output of an accurate 7.5-V voltage reference. This output is capable of delivering 10 mA to peripheral circuitry and is internally short-circuit current limited. VREF is disabled and remains at 0 V when VCC is below the UVLO threshold. Bypass VREF to GND with a 0.1- $\mu$ F or larger ceramic capacitor for best stability.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## block diagram

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

**TYPICAL CHARACTERISTICS**

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# TYPICAL APPLICATION

The UCC38500 series is designed to incorporate all the control functions required for a power factor correction circuit and a second stage dc-to-dc converter. The PFC function is implemented as a full-feature, average-current-mode controller integrated circuit. In addition, the input voltage feedforward function is implemented in a simplified manner. Current from IAC input is mirrored over to the VFF pin. By simply adding a resistor and capacitor (to attenuate 120-Hz ripple) a voltage is developed which is proportional to RMS line voltage, eliminating the need for several components normally connected to the line.

The UCC3850x uses leading-edge modulation for the PFC stage and trailing-edge modulation for the dc-to-dc stage. This reduces ripple current in the output capacitor by reducing the overlap in conduction time of the PFC and dc-to-dc switches. Figures 7 and 8 depict the ripple current reduction in the boost switch. In addition to the reduced ripple current, noise immunity is improved through the current error amplifier implementation. Please refer to the UCC3817 datasheet (TI Literature No. SLUS395) for a detailed explanation of current error amplifier implementation.

UDG-97130-1

Figure 7. Simplified Representation of a 2–Stage PFC Power Supply

Figure 8. Timing Waveforms for Synchronization Scheme

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

# **TYPICAL APPLICATION**

The UCC3850x is optimized to control a boost PFC stage operating in continuous conduction mode, followed by a dc-to-dc converter (typically a forward topology). The dc-to-dc converter is transformer isolated and therefore its error amplifier is located on the secondary side. For this reason the UCC3850x is configured without an internal error amplifier for the second power stage. The externally generated error signal is fed into the VERR pin typically through an opto coupler.

The UCC3850x can be configured for voltage-mode control or current-mode control of the second stage. The application figure shows a typical current-mode configuration. For voltage-mode control, the ramp generated by CT can be fed back into the ISENSE2 pin through a voltage divider.

One of the main system challenges in designing systems with a PFC front end is coordinating the turn-on and turn-off on the dc-to-dc converter. If the dc-to-dc converter is allowed to turn on before the boost converter is operational, it must operate at a much-reduced voltage and therefore represents a large current draw to the boost converter. This start-up sequencing is handled internally by the UCC3850x. The UCC3850x monitors the output voltage of the PFC converter and holds the dc-to-dc converter off until the output is within 10% of its regulation point. Once the trip point is reached the dc-to-dc section goes through a soft start sequence for a controlled, low stress start-up. Similarly, if the output voltage drops too low (two voltage options are available) the dc-to-dc converter shuts down thereby preventing overstress of the converter. For the UCC38500 and UCC38501, the dc-to-dc converter shuts down when the PFC output falls below 74% of its nominal value, while for the UCC38502 and UCC38503, the threshold is lowered to 50%.

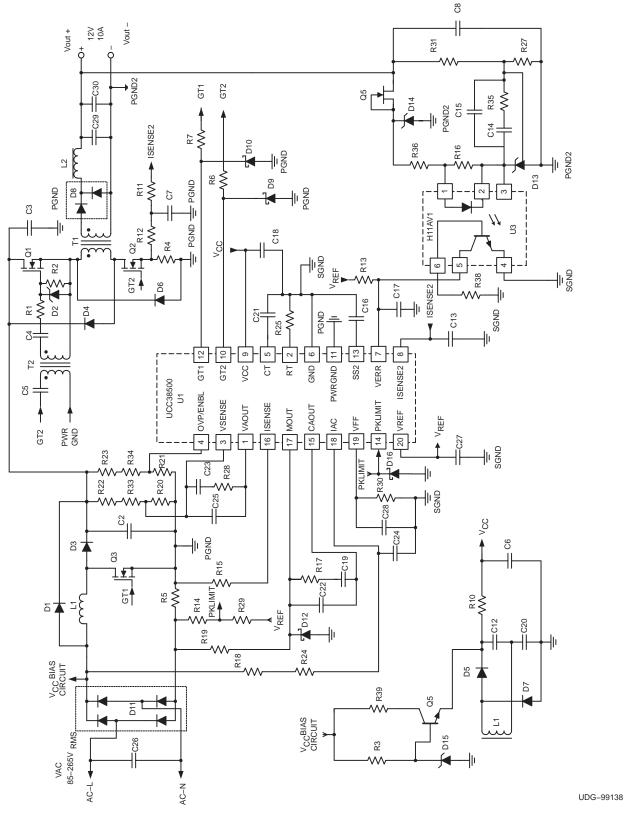

## design example: an off-line, 100-W, power converter

The following design example shows how to implement the UCC38500 in an off-line 100-W power converter. The system requires the converter to operate from a universal input of 85 V<sub>RMS</sub> to 265 V<sub>RMS</sub> with a 12-V, 100-W, dc output. This design example is divided into two parts. The first part is the PFC stage design and the second section is the dc-to-dc power stage design. The design goal of the system is to achieve an efficiency of approximately 80%. This is accomplished by requiring the boost regulator to be designed for an efficiency of 95% and the dc-to-dc power stage to be designed for 85% efficiency. The efficiency of the boost converter is designated by variable  $\eta$ 1 and the efficiency of the dc-to-dc converter is designated by variable  $\eta$ 2. Figure 9 shows the schematic of the typical application upon which this design example is based. The UCC38500 control device is chosen for this design because of it's self-biasing scheme and minimum input voltage requirements of the dc-to-dc power stage.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

**Figure 9. Typical Application Circuit**

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## TYPICAL APPLICATION

## I. PFC Boost Power Stage

## LBOOST (L1 in Figure 9)

The boost inductor value is determined by the following equations:

$$\Delta I = \frac{\frac{P_{OUT} \times (0.25) \times \sqrt{2}}{\eta 1 \times \eta 2}}{V_{IN (min)}} , \qquad (1)$$

$$D = 1 - \frac{V_{IN \text{ (min)}} \times \sqrt{2}}{V_{BOOST}}, \qquad (2)$$

$$L_{\text{BOOST}} = \frac{V_{\text{IN (min)}} \times \sqrt{2} \times D}{\Delta I \times f_{\text{S}}}$$

(3)

where  $\Delta I$ , the inductor current ripple was set to approximately 25% of the peak inductor current.

In this design example  $\Delta I$  is approximately 505 mA. D represents the duty cycle at the peak of low line voltage,  $V_{IN(min)}$  is the minimum RMS input voltage, and  $V_{BOOST}$  is the controlled output voltage of the PFC stage.  $V_{BOOST}$  for this design is selected to be 385 V to ensure the PFC stage regulates for the full input voltage range. Variable  $f_S$  represent the switching frequency. The switching frequency was selected to be 100 kHz for this design. The calculated boost inductor required for this design is approximately 1.7 mH.

#### CBOOST (C2 in Figure 9)

Two main criteria, the capacitance and the voltage rating, dictate the selection of the output capacitor. The value of capacitance is determined by the holdup time required for supporting the load after the input ac voltage is removed. Holdup is the amount of time that the output stays in regulation after the input has been removed. For this circuit, the desired holdup time is approximately 16 ms. Expressing the capacitor value in terms of output power, output voltage, and holdup time is described in equation (4):

$$C_{BOOST} = \frac{2 \times P_{OUT} \times \Delta t}{\left(V_{BOOST}\right)^2 - \left(V_{BOOST (min)}\right)^2}$$

(4)

In practice, the calculated minimum capacitor value may be inadequate because output ripple voltage specifications limit the amount of allowable output capacitor ESR. Attaining a sufficiently low value of ESR often necessitates the use of a much larger capacitor value than calculated. The amount of output capacitor ESR allowed is determined by dividing the maximum specified output ripple voltage by the capacitor ripple current. In this design, holdup time is the dominant determining factor and a 100  $\mu$ F, 450 V aluminum electrolytic capacitor from Panasonic, part number ECOS2TB101BA, is used. The voltage rating and the low ESR of 0.663  $\Omega$  make it an ideal choice for this design.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## TYPICAL APPLICATION

## power switch selection (Q3 in Figure 9)

As in any power supply design, tradeoffs between performance, cost and size are necessary. When selecting a power switch, it is useful to calculate the total power dissipation in the switch for several different devices at the switching frequencies being considered for the converter. Total power dissipation in the switch is the sum of switching loss and conduction loss. Switching losses are the combination of the gate charge loss, drain source capacitance of the MOSFET loss and turnon and turnoff losses:

$$P_{GATE} = Q_{GATE} \times V_{GATE} \times f_{S}$$

(5)

$$P_{COSS} = \frac{1}{2} C_{OSS} \left( V_{OFF} \right)^2 \times f_S$$

(6)

$$P_{SW} = \frac{1}{2} V_{OFF} \times I_{L} \times (t_{ON} + t_{OFF}) \times f_{S}$$

(7)

Where  $Q_{GATE}$  is the total gate charge,  $V_{GATE}$  is the gate drive voltage,  $f_s$  is the switching frequency,  $C_{OSS}$  is the drain source capacitance of the MOSFET,  $t_{ON}$  and  $t_{OFF}$  are the switching times (estimated using device parameters  $R_{GATE}$ ,  $Q_{GD}$  and  $V_{TH}$ ) and  $V_{OFF}$  is the voltage across the switch during the off time, in this case  $V_{OFF} = V_{BOOST}$ .

Conduction loss is calculated as the product of the  $R_{DS(on)}$  of the switch (at the worst case junction temperature) and the square of RMS current:

$$P_{COND} = R_{DS(on)} \times K \times (I_{RMS})^2$$

(8)

where K is the temperature factor found in the manufacturer's R<sub>DS(on)</sub> vs junction temperature curves.

Calculating these losses and plotting against frequency gives a curve that enables the designer to determine either which manufacturer's device has the best performance at the desired switching frequency, or which switching frequency has the least total loss for a particular power switch. For this design example an IRFP450 HEXFET from International Rectifier is chosen because of its low  $R_{DS(on)}$  and its  $V_{DSS}$  rating. The IRFP450's  $R_{DS(on)}$  of 400 m $\Omega$  and the maximum  $V_{DSS}$  of 500 V makes it an ideal choice. A comprehensive review of this procedure can be found in the Unitrode Power Supply Design Seminar SEM–1200, Topic 6, TI Literature No. SLUP117.

More recently, faster switching insulated gate bipolar transistors (IGBTs) have become widely available. Depending on the system power level (and the switching frequency), use of IGBTs may make sense for the power switch.

#### boost diode selection (D3 in Figure 9)

In order to keep the switching losses to a minimum and meet the voltage and current requirements, a HFA08TB60 fast recovery diode from International Rectifier is selected for the design. This diode is rated for a maximum reverse voltage of 600 V and a maximum forward current of 8 A. The typical reverse recovery of 18 ns made this diode ideal for this design.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

#### peak current limit

Resistor divider R14 and R29 along with current sense resistor R5, devise the peak-limit comparator of the UCC38500 and are used to protect the boost switch Q3 from excessive currents. Proper preparation of this comparator requires that it not interfere with the boost converter's power limit or the forward converter's pulse-by-pulse current limiting. For this design example the forward converter is selected to go into pulse-by-pulse current limiting at approximately 130% of maximum output power. The power limit of the boost converter is selected to a selected to engage at 140% of the maximum output power. The peak current limit for the boost stage was selected to engage at 150% of the maximum output power to ensure circuit stability.

The following equation is used to select the current-sense resistor R5, where the current-sense resistor is selected to operate over a 1-V dynamic range ( $V_{DYNAMIC}$ ). The current-sense resistor required for the design needed to be approximately 0.43  $\Omega$ .

$$R5 = R_{SENSE} = \frac{V_{DYNAMIC}}{I_{PK} + (0.5) \times \Delta I} \approx 0.43 \Omega$$

(9)

The following equation is used to size resistor R14 properly by first selecting R29 to be a standard resistance value. For this design resistor R29 was selected to be 10 k $\Omega$ . With a typical reference voltage (V<sub>REF</sub>) of 7.5 V gives a calculated value of approximately 1.91 k $\Omega$  for resistor R14.

$$R14 = \frac{\left(\frac{P_{OUT} \times 1.5 \times \sqrt{2}}{V_{IN \text{ (min)}} \times \eta 1 \times \eta 2} + \Delta I\right) \times R5 \times R29}{V_{REF}}$$

(10)

#### multiplier

The output of the multiplier of the UCC38500 is a signal representing the desired input line current. It is an input to the current amplifier, which programs the current loop to control the input current to give high power-factor operation. As such, the proper functioning of the multiplier is key to the success of the design. The inputs to the multiplier are  $V_{VAOUT}$ , the voltage amplifier output,  $I_{IAC}$ , a representation of the input rectified ac line voltage, and an input voltage feed forward signal,  $V_{VFF}$ . The output of the multiplier,  $I_{MOUT}$ , can be expressed:

$$I_{MOUT} = \frac{I_{IAC} \times (V_{VAOUT} - 1)}{K \times (V_{VFF})^2}$$

(11)

Where K is a constant typically equal to 1 / V.

The I<sub>IAC</sub> signal is obtained through a high-value resistor connected between the rectified ac line and the IAC pin of the UCC3850X. This resistor (R<sub>IAC</sub>) is sized to provide the maximum I<sub>IAC</sub> current at high line. For the UCC3850X the maximum I<sub>IAC</sub> current is about 500  $\mu$ A, and a higher current can drive the multiplier out of its linear range. A smaller current level is functional, but noise can become an issue, especially at low input line. Assuming a universal line operation of 85 V<sub>RMS</sub> to 265 V<sub>RMS</sub> gives a R<sub>IAC</sub> value of 750 kΩ. Because of voltage rating constraints of the standard 1/4-W resistor, this application requires a combination of lower value resistors connected in series to give the required resistance and distribute the high voltage amongst the resistors. For this design example two 383 kΩ resistors are used in series.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## TYPICAL APPLICATION

The current into the IAC pin is mirrored internally to the VFF pin where it is filtered to produce a voltage feed forward signal proportional to line voltage. The VFF voltage is used to keep the power stage gain constant and to providing input power limiting. Please refer to Texas instruments Application Note on *Power Limiting with Sinusoidal Input* TI Literature No. SLUA196, for detailed explanation on how the VFF pin provides power limiting. The following equation is used to determine the VFF resistor size ( $R_{VFF}$ ) to provide power limiting where  $V_{IN(min)}$  is the minimum RMS input voltage and  $R_{IAC}$  is the total resistance connected between the IAC pin and the rectified line voltage.

$$R_{VFF} = \frac{1.4 \text{ V}}{\left(\frac{\text{V}_{\text{IN} (\text{min})} \times 0.9}{2 \times \text{R}_{\text{IAC}}}\right)} \cong 28.7 \text{ k}\Omega$$

(12)

Because the VFF voltage is generated from line voltage it needs to be adequately filtered to reduce total harmonic distortion caused by the 120-Hz rectified line voltage. Refer to Unitrode Power Supply Design Seminar, SEM–700 Topic 7, *Optimizing a High Power Factor Switching Preregulator*, TI Literature No. SLUP093. A single pole filter is adequate for this design. Assuming that an allocation of 1.5% total harmonic distortion from this input is allowed, and that the second harmonic ripple is 66% of the input ac line voltage, the amount of attenuation required by this filter is:

$$\frac{1.5\%}{66\%} = 0.022 \tag{13}$$

With a ripple frequency ( $f_R$ ) of 120-Hz and an attenuation of 0.022 requires that the pole of the filter ( $f_P$ ) be placed at:

$$f_{\rm P} = 120 \,\text{Hz} \times 0.022 \cong 2.6 \,\text{Hz}$$

(14)

The following equation is used to select the filter capacitor (C<sub>VFF</sub>) required to produce the desired low pass filter.

$$C_{VFF} = \frac{1}{2\pi \times R_{VFF} \times f_P} \cong 2.2 \,\mu\text{F}$$

(15)

This results in a single-pole filter, which adequately attenuates the harmonic distortion and provides power limiting.

The R<sub>MOUT</sub> resistor is sized to provide power limiting for the circuit. The power limit is set to 140% of the maximum output power. This is done so that the power limit of the PFC stage does not interfere with power limiting of the dc-to-dc converter, which is set to 130% of the maximum output power. The following equations are used to size the R<sub>MOUT</sub> resistor, R19. In these equations P<sub>LIMIT</sub> is the power limit level, P<sub>OUT</sub> is the maximum output power. I<sub>MOUT</sub> is the maximum multiplier output current, I<sub>IAC</sub>@V<sub>IN(min)</sub> is the minimum current into the IAC pin at low line and V<sub>VAOUT</sub>(max) is the maximum voltage amplifier output voltage. For this design R19 and R15 need to be approximately 3.57 kΩ.

$$\mathsf{P}_{\mathsf{LIMIT}} = \frac{\mathsf{P}_{\mathsf{OUT}} \times 1.4}{\eta 1 \times \eta 2} \tag{16}$$

$$I_{MOUT(max)} = \frac{I_{IAC} @ V_{IN(min)} \times (V_{VAOUT(max)} - 1 V)}{K \times (V_{FF})^2}$$

(17)

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

$\mathsf{R}_{MOUT} = \frac{\frac{\mathsf{P}_{LIMIT} \times \sqrt{2} \times \mathsf{R}_{SENSE}}{\mathsf{V}_{IN \; (min)}}}{\mathsf{I}_{MOUT(max)}}$

(18)

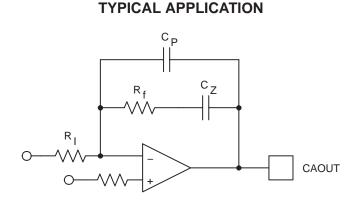

#### current loop

The UCC38500 current amplifier has the input from the multiplier applied to the inverting input. This change in architecture from previous Texas Instruments PFC controllers improves noise immunity in the current amplifier. It also adds a phase inversion into the control loop. The UCC38500 takes advantage of this phase inversion to implement leading-edge duty cycle modulation. Please refer to Figure 10 for the typical configuration of the current amplifier.

The following equation defines the gain of the power stage, where  $V_P$  is the voltage swing of the oscillator ramp, 4 V for the UCC38500.

$$G_{ID}(s) = \frac{V_{BOOST} \times R_{SENSE}}{s \times L_{BOOST} \times V_{P}}$$

(19)

In order to have a good dynamic response the crossover frequency of the current loop was set to 10% of the switching frequency. This can be achieved by setting the gain of the current amplifier ( $G_{CA}$ ) to the inverse of the current loop power stage gain at the crossover frequency. This design requires that the current amplifier have a gain of 2.581 at 10 kHz.

$$G_{CA} = \frac{1}{G_{ID}(s)} = 2.581$$

(20)

$R_I$  is the  $R_{MOUT}$  resistor, previously calculated to be 3.57 k $\Omega$  (refer to Figure 10). The gain of the current amplifier is  $R_F/R_I$ , so multiplying  $R_I$  by  $G_{EA}$  gives the value of  $R_F$ , in this case approximately 9.09 k $\Omega$ . Setting a zero at the crossover frequency and a pole at half the switching frequency to roll off the high-frequency gain completes the current loop compensation.

$$C_{Z} = \frac{1}{2\pi \times R_{F} \times f_{C}}$$

(21)

$$C_{\rm P} = 2\pi \times R_{\rm F} \times \left(\frac{f_{\rm S}}{2}\right)$$

(22)

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

Figure 10. Current Loop Compensation

## voltage loop

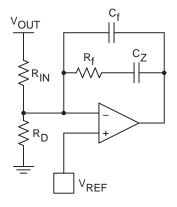

The second major source of harmonic distortion is the ripple on the output capacitor at the second harmonic of the line frequency. This ripple is fed back through the error amplifier and appears as a 3rd harmonic ripple at the input to the multiplier. The voltage loop must be compensated not just for stability but also to attenuate the contribution of this ripple to the total harmonic distortion of the system (refer to Figure 11).

#### Figure 11. Voltage Amplifier Configuration

The gain of the voltage amplifier,  $G_{VA}$ , can be determined by first calculating the amount of peak ripple present on the output capacitor  $V_{OPK}$ . The peak value of the second harmonic voltage is given by equation (23), where  $f_R$  is the frequency of the rectified line voltage. For this design  $f_R$  is equal to 120 Hz.

$$V_{OPK} = \frac{P_{IN}}{\left(2 \ \pi \times f_{R} \times C_{BOOST} \times V_{BOOST}\right)}$$

(23)

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

In this example V<sub>OPK</sub> is equal to 4 V. Assuming an allowable contribution of 0.75% (1.5% peak-to-peak) from the voltage loop to the total harmonic distortion budget sets the gain equal to:

$$G_{VA} = \frac{\left(\Delta V_{VAOUT}\right)(0.015)}{2 \times V_{OPK}}$$

(24)

Where  $\Delta V_{VAOUT}$  is the effective output voltage range of the error amplifier (5 V for the UCC38500). The network needed to realize this filter is comprised of an input resistor, R<sub>IN</sub>, and feedback components C<sub>F</sub>, C<sub>Z</sub>, and R<sub>F</sub>. The value of R<sub>IN</sub> is already determined because of its function as one-half of a resistor divider from V<sub>OUT</sub> feeding back to the voltage amplifier for output voltage regulation. In this case the value is 1.12 M $\Omega$ . This high value was chosen to reduce power dissipation in the resistor. In practice, the resistor value would be realized by the use of two 560-k $\Omega$  resistors in series because of the voltage rating constraints of most standard 1/4 W resistors. The value of C<sub>F</sub> is determined by the equation:

$$C_{F} = \frac{1}{\left(2\pi \times f_{R} \times G_{VA} \times R_{IN}\right)}$$

(25)

In this example  $C_F$  equals 150 nF. Resistor  $R_F$  and  $C_F$  generate a pole in the voltage amplifier feedback to reduce total harmonic distortion (THD). The location of the pole is found by setting the gain of the loop equation to one and solving for the crossover frequency. The frequency, expressed in terms of input power, is calculated by the equation:

$$f_{VI} = \frac{\sqrt{P_{IN}}}{2\pi \sqrt{\Delta V_{VAOUT} \times V_{OUT} \times R_{IN} \times C_{BOOST} \times C_{F}}}$$

(26)

f<sub>VI</sub> for this converter is 10 Hz. A derivation of this equation can be found in the Unitrode Power Supply Design Seminar SEM–1000, Topic 1, *Power Factor Correction Circuit,* TI Literature No. SLUP106.

Solving for R<sub>F</sub> becomes:

$$R_{F} = \frac{1}{\left(2\pi \times f_{VI} \times C_{F}\right)}$$

(27)

Or  $R_F$  equals approximately 118 k $\Omega$ .

Due to the low output impedance of the voltage amplifier, capacitor  $C_Z$  is added to improve dc regulation. To maintain good phase margin, the zero from  $C_Z$  is set to 10% of  $f_{VI}$ . For this design,  $C_Z$  is a 2.2- $\mu$ F capacitor. The following equation is used to calculate  $C_Z$ .

$$C_{Z} = \frac{1}{2\pi \times \left(\frac{f_{VI}}{10}\right) \times R_{F}}$$

(28)

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## TYPICAL APPLICATION

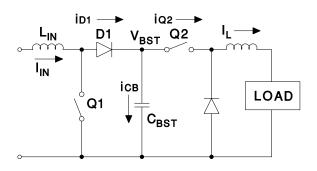

## II. Two Switch Forward DC-to-DC Power Stage

A two-switch forward converter topology was selected for the second stage of this design. The two-switch forward power converter has two major advantages over a traditional forward converter, making it ideal for this application. First, the FETs used in the two-switch forward required only one-half the maximum  $V_{DS}$  as compared to the traditional forward converter. Second, the transformer's reset energy is returned to the input through clamping diodes for higher efficiency.

#### transformer turns ratio

Equation (29) calculates the transformer turns ratio required for the two-switch forward power converter of this design example. It can be derived from the dc transfer function of a forward converter.  $V_{OUT}$  is the output voltage of the forward converter and is 12-V for this design.  $V_F$  is the forward voltage drop of the secondary rectifier diode and is set to 1V.  $V_{BOOST(min)}$  is the minimum input voltage to the forward converter. The level of this voltage is determined by where the control device forces the dc-to-dc converter into undervoltage lockout (UVLO). The UCC38500 control device is configured to drive the dc-to-dc power stage into UVLO at approximately 74% of the nominal boost converters output voltage.  $V_{BOOST(min)}$  for this design is approximately 285 V.  $D_{MAX}$  is 0.44 and is the guaranteed maximum duty cycle of the forward converter. For this design example the calculated turns ratio is approximately 0.101.

Transformer Turns =

$$\frac{V_{OUT} + V_F}{V_{BOOST(min)} \times D_{MAX}} = \frac{N_S}{N_P}$$

(29)

#### output inductor

The following equations can be used to calculate the inductor required for this design example. First, the minimum duty cycle  $D_{MIN}$ , which occurs at the maximum boost voltage, needs to be calculated. The maximum boost voltage is limited by the OVP trip point, which is set to approximately 425 V. For this design  $D_{MIN}$  is approximately 31%. The output inductor ripple current ( $\Delta I_L$ ) for this design is given at 30% of the maximum load current. Next calculate the output inductor (L), where the switching frequency (f<sub>S</sub>) is 100 kHz. The calculated output inductor for this design is approximately 38  $\mu$ H.

$$D_{MIN} = \frac{V_{OUT} + V_F}{V_{BOOST(max)}} \times \frac{N_P}{N_S}$$

(30)

$$\Delta I_{L} = \frac{P_{OUT} \times 0.3}{V_{OUT}}$$

(31)

$$L = \frac{\left(V_{OUT} + V_{F}\right) \times \left(1 - D_{MIN}\right)}{\Delta I_{L} \times f_{S}}$$

(32)

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

#### output capacitor

The following equations can be used to estimate the minimum output capacitance and the capacitor's maximum allowable equivalent series resistance (ESR), where  $C_{OUT}$  is the minimum output capacitance and t<sub>S</sub> is the period of the switching frequency.  $\Delta V_{OUT}$  is the maximum allowable output ripple voltage, selected as approximately 1% of the output voltage. For this design, the minimum calculated output capacitance is 170 µF and the maximum allowable ESR is 96 m $\Omega$ . A Panasonic HFQ 1800-µF electrolytic capacitor with an ESR of 0.048  $\Omega$  is used.

$$C_{OUT} = \frac{1}{8} \times \frac{\left(V_{OUT} + V_{F}\right) \times \left(D_{MAX} \times \left(t_{S}\right)^{2}\right)}{L \times \Delta V_{OUT}}$$

(33)

$$\mathsf{ESR} = \frac{-\mathbf{OOT}}{\Delta \mathsf{I}_{\mathsf{L}}} \tag{34}$$

## R<sub>SENSE2</sub>

The dc-to-dc power converter is designed for peak current mode control.  $R_{SENSE2}$  is the resistor that senses the current in the forward converter. The sense resistor in Figure 9 is referred to as R4. The following equations can be used to calculate  $R_{SENSE2}$ . Where  $I_M$  is the magnetizing current of the transformer used in the step-down converter and  $V_{BOOST}$  is the output voltage of the boost stage. D is the typical duty ratio of the forward converter.  $V_{ISENSE2\_peak}$  is the peak current sense comparator voltage that is typically 1.15 V. For this design example  $L_M$  is approximately 8 mH and the  $R_{SENSE2}$  is approximately 1  $\Omega$ .

$$I_{M} = \frac{V_{BOOST}}{L_{M}} \times \frac{D}{f_{S}}$$

(35)

$$R_{SENSE2} = \frac{V_{ISENSE2\_peak}}{I_{M} + \frac{N_{S}}{N_{P}} \left(\frac{\Delta I_{L}}{2} + I_{OUT(max)} \times 1.3\right)}$$

(36)

#### soft-start

The UCC38500 has soft-start circuitry to allow for a controlled ramp of the second stage's duty cycle during start-up. This is accomplished through the SS2 circuitry described earlier in this data sheet. Equation (37) calculates the approximate capacitance needed based on the designer's soft-start requirements. Where I<sub>SS2</sub> is the soft-start charging current, which is typically 10  $\mu$ A.  $\Delta t$  is the desired soft start time, which was selected to be approximately 5 ms for this example. The calculated soft-start capacitor (C<sub>SS</sub>) for this example is approximately 10 nF.

$$C_{SS} = \frac{I_{ISS2} \times \Delta t}{4.5}$$

(37)

#### slope compensation

When designing with peak current-mode control, slope compensation may be necessary to prevent instability. In this design, the magnetizing current provided more than enough slope compensation. If slope compensation is needed with external components, please refer to Unitrode/Texas Instruments Application Note, *Practical Considerations in Current Mode Power Supplies*, TI Literature No. SLUA110.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## TYPICAL APPLICATION

#### control loop

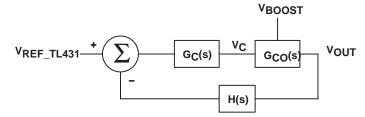

Figure 12 shows the control block diagram for the typical application shown in Figure 9.  $G_C(s)$  is the compensation network's transfer function (TF),  $G_{OPTO}(s)$  is the opto-isolator TF,  $G_{CO}(s)$  is the control-to-output TF, and H(s) is the divider TF. The following equations can be used to estimate the frequency response of each gain block, where  $f_{OPTO_pole}$  is the frequency, where the optoisolator is –3 dB from its dc operating point, and  $V_{REF_TL431}$  is the reference voltage of the TL431 shunt regulator.  $R_{LOAD}$  represents the typical load impedance for the design.

$$G_{OPTO}(s) = \frac{R13}{R36} \times \frac{1}{1 + \frac{s}{2\pi \times f_{OPTO\_pole}}}$$

(38)

$$G_{C}(s) = \frac{s \times R35 \times C14 + 1}{s \times C14 \times R31 \times (1 + (s \times R35 \times C15))} \times \frac{R13}{R36} \times \frac{1}{1 + \frac{s}{2\pi \times f_{OPTO\_pole}}}$$

(39)

$$H(s) = \frac{R27}{R27 + R31} = \frac{V_{VREF_TL431}}{V_{OUT}}$$

(40)

$$G_{CO}(s) = \frac{V_{OUT}}{V_{C}} = \frac{R_{LOAD}}{R_{SENSE2}} \times \frac{N_{P}}{N_{s}} \times \frac{\left(1 + \left(s \times C_{OUT} \times ESR\right)\right)}{\left(1 + \left(s \times C_{OUT} \times R_{LOAD}\right)\right)}$$

(41)

Figure 12. UCC38500 Control Block

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

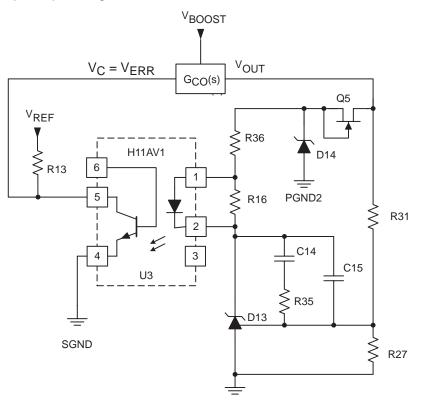

Figure 13 shows the circuitry for the voltage feedback loop. D13 is a TL431 shunt regulator that functions as an operational amplifier, providing feedback control.

UDG-01091

Figure 13. UCC38500 Feedback Loop

Initially the designer must select the resistor values for the divider gain H(s). Equation (42) is used to determine resistor size. Selecting R27 to be a standard value of  $10-k\Omega$  requires R31 to be approximately 38.3 k $\Omega$ .

$$R31 = \frac{R27 \left(V_{OUT} - V_{REF}\right)}{V_{REF}}$$

(42)

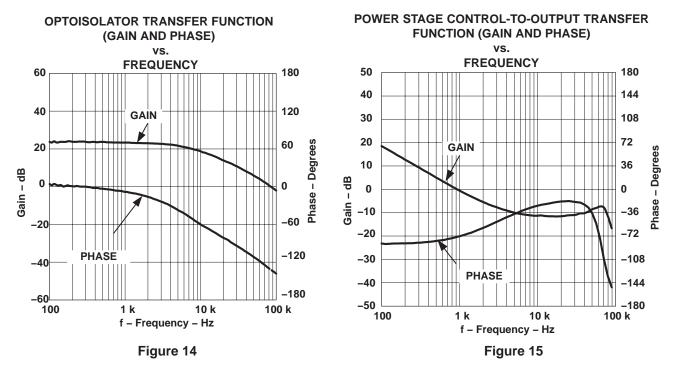

It is important to correctly bias the TL431 and the optoisolator for proper operation. Zener diode D14 and a depletion mode J-FET, Q5, supply the bias voltage for the TL431. Resistors R16 and R13 provide the minimum bias currents for the TL431 and the optoisolator respectively and can be calculated with the following equations. Where  $I_{OP(min)}$  is the minimum optoisolation current, and  $V_{VERR(max)}$  is the maximum voltage seen at the VERR pin of the UCC38500. VERR has an internal clamp that limits this pin to 4.5 V.  $V_F$  is the typical forward voltage of the diode in the opto isolator, and  $I_{TL431(min)}$  is the minimum cathode current of the TL431. For the components used in this design example R13 is calculated to be approximately 2.0 k $\Omega$  and R16 was calculated to be approximately 680  $\Omega$ . The optoisolator is configured to have dc gain of approximately 20 dB and the optoisolator –3 dB point is approximately 8 kHz. Figure 14 shows the frequency response of the optoisolator.

SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

## **TYPICAL APPLICATION**

$$R16 = \frac{V_{F}}{I_{TL431 \text{ (min)}}}$$

$$R13 = \frac{V_{REF} - V_{VERR \text{ (max)}}}{I_{OP \text{ (min)}}}$$

(43)

(44)

To compensate the loop, it is necessary to estimate or measure the control-to-output gain's frequency response  $G_{CO}(s)$ . The frequency response for  $G_{CO}(s)$  was measured with a network analyzer and the measured frequency response is shown in Figure 15.

After determining the frequency response of  $G_{CO}(s)$  it is necessary to define some closed loop frequency response design goals. The following equation describes the frequency response of the loop gain  $(T(s)_{dB})$  of the system in decibels. Typically, the loop is designed to crossover at a frequency below one-sixth of the switching frequency. In order for this design example to have good transient response, the design goal is to have the loop gain crossover at approximately 1 kHz, which is less than one-sixth of the switching frequency. The gain crossover frequency for this design example is referenced as  $f_C$ .

$$T(s) dB = G_{C}(s) + G_{CO}(s) + H(s)$$

(45)

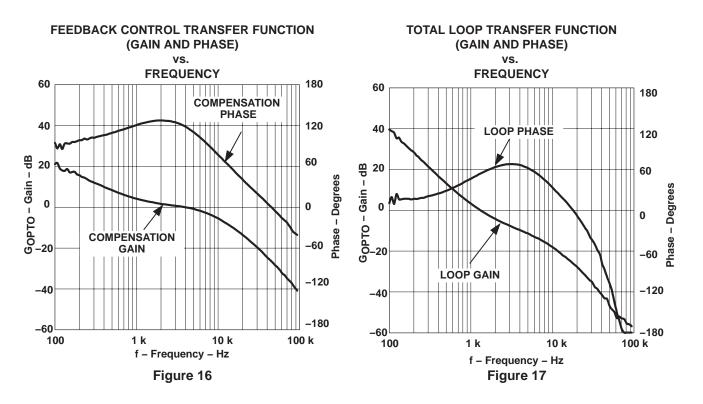

The compensation network that is used ( $G_C(s)$ ) has three poles and one zero. One pole occurs at the origin, and a second pole is caused by the limitations of the opto-isolator. The third pole is set to attenuate the high-frequency gain and needs to be set to one-half of the switching frequency. The zero is set at the desired crossover frequency.

The following equations can be used to select R35, C14 and C15, where  $G_{CO}(s)$ ,  $G_{OPTO}(s)$ , and H(s) are the gains in decibels (dB) of each control block at the desired  $f_C$ . From the graphs in Figures 14 and 15 it can be observed at the desired crossover frequency  $G_{CO}(s)$  is approximately 0 dB and  $G_{OPTO}(s)$  is approximately

#### SLUS419C - AUGUST 1999 - REVISED NOVEMBER 2001

23 dB. Therefore the compensation circuitry needs to have a gain of -23 dB at the desired crossover frequency. For this example R35 is calculated at approximately 18.2 k $\Omega$ . Capacitor C14 is estimated to be approximately 10 nF and C15 is calculated at approximately 180 pF.

$$H(s) = 20 \log \left[ \frac{V_{\text{REF}}}{V_{\text{OUT}}} \right]$$

(46)

$R35 = R31 \times 10^{(-G_{CO}(s) dB + G_{OPTO}(s) dB + H(s) dB)}$

$$C14 = \frac{1}{\left(2\pi \times R35 \times f_{C}\right)}$$

(48)

(47)

$$C15 = \frac{1}{\left(2\pi \times R35 \times \frac{f_{SW}}{2}\right)}$$

(49)

Figure 16 shows the frequency response of the compensation network  $G_C(s)$  and Figure 17 shows the measured frequency response of the loop gain T(s). The frequency response characteristics in Figure 17 show that  $f_C$  is approximately 1.5 kHz with a phase margin of about 55 degrees. The gain margin is approximately 50 dB.

NSTRUMENTS

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| UCC28500DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28500DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28500N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC28501DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28501DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28501N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC28502DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28502DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28502N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC28503DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28503DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC28503N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC38500DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38500DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38500N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC38501DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38501DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38501N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC38502DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38502DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38502N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

| UCC38503DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38503DWTR     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | None                    | CU SNPB          | Level-2-220C-1 YEAR          |

| UCC38503N        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | None                    | CU SNPB          | Level-NA-NA-NA               |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - May not be currently available - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

None: Not yet available Lead (Pb-Free).

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean "Pb-Free" and in addition, uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

# PACKAGE OPTION ADDENDUM

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

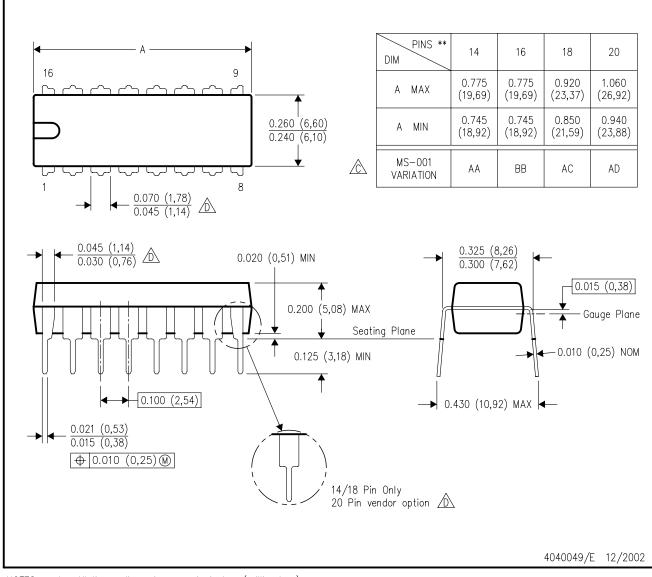

# N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

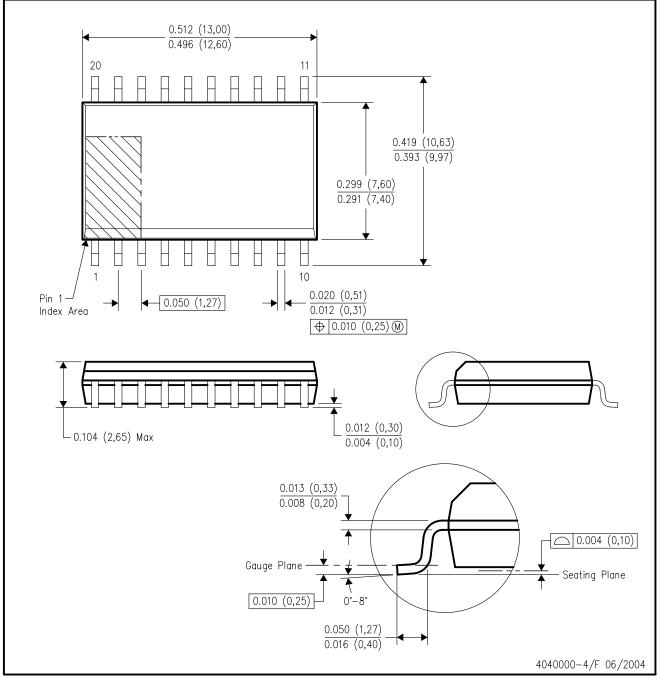

DW (R-PDSO-G20)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AC.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated