# LSI/CSI LS7222

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

## **KEYPAD PROGRAMMABLE DIGITAL LOCK**

#### FEATURES:

- Stand alone lock logic

- 38416, 4-digit combinations

- 3 different user programmable codes

- Momentary and static lock control outputs

- Internal key debounce circuitry

- Tamper detection output

- Status outputs

- Low current consumption

- +4V to +15V operation (VDD -Vss)

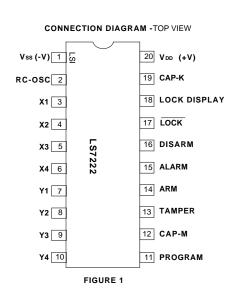

- LS7222 (DIP), LS7222-S (SOIC)- See Figure 1

#### **GENERAL DESCRIPTION:**

The LS7222 is a programmable electronic lock implemented in a monolithic CMOS integrated circuit. The circuit contains all the necessary memory, decoder and control logic to make a programmable "keyless" lock system to control electro-mechanical locks. Input is provided by a matrix keypad whose maximum allowable size is 4 x 4.

The LS7222 can be programmed to recognize 3 different codes: one to lock (Arm), one to unlock (Disarm), and one to unlock and trigger an alarm (Duress). Programming is done via the keypad inputs. Any entry from the keypad (when not in the program mode) which does not match one of the 3 programmed codes causes the Tamper output to become active.

The monolithic, low power CMOS design of the LS7222 enables it to be designed into typical battery backed-up and automotive type security systems.

#### **DETAILED DESCRIPTION:**

CODES - There are 3 different function codes which the LS7222 can store in memory. Each code consists of a 4-digit number which must be entered in exact sequence and before the keypad entry enable time expires. The 3 codes and their functions are explained below.

1. The Arm code, when entered from the keypad, causes the Lock output to latch low and the Arm output to momentarily go high. Whenever power is first applied to the LS7222, the circuit defaults to the Arm code corresponding to the keys X1 Y1, X1 Y2, X2 Y2, X2 Y1. The code can then be altered to any other 4 digit code by entering the Program Mode and keying in the new code.

- 2. The Disarm code, when entered from the keypad, causes the Lock output to latch high and the Disarm output to momentarily go high. The first 3 digits of the Disarm code must be identical to the first 3 digits of the Arm code; the 4th digit may or may not be identical for the two codes. When the two codes are the same in all 4 digits, i.e. the same code is chosen for arming and disarming, the entry of the code will cause the Lock output to toggle. This means that if the output was high (unlocked) it will go low (locked) and vice-versa. Whenever power is first applied to the LS7222, the circuit defaults to the Disarm code corresponding to the keys X1 Y1, X1 Y2, X2 Y2, X1 Y1. The code can then be altered by entering the Program mode.

- 3. The Duress code, when entered from the keypad, causes the Lock output to latch high and the Disarm output to momentarily go high; at the same time the Alarm output will latch high to enable an external alarm. The first 3 digits of the Duress code must be identical to the first 3 digits of the Arm and Disarm codes; the 4th digit must be different to activate the Alarm output. Whenever power is first applied to the LS7222, the circuit defaults to the Duress code corresponding to the keys X1 Y1, X1 Y2, X2 Y2, X1 Y2. The code can then be altered the same way as the other two codes.

December 2002

**Program Mode** - The current Arm/Disarm/Duress codes may be altered to any value by initializing the Program mode. The steps involved for altering the codes are:

- 1. Enter the current Disarm code causing the Disarm output to go high.

- 2. Before the keypad entry enable time expires, enter the key corresponding to matrix position X4 Y1 two times. This will cause the Program Mode output to latch high, indicating that the circuit is now in the Program mode. The keypad entry enable timer is disabled during the Program mode.

- 3. Enter a 6-digit number from the keypad. The Program Mode output will latch low, indicating that the new codes have successfully been programmed. Of the 6 digits, the first 4 constitute the Arm code; the first 3 and the 5th constitute the Disarm code and the first 3 and the 6th constitute the Duress code. If an error is introduced or it is desired to change the codes before the 6th digit is typed, enter the key X4 Y3. This will reset the internal memory pointer of the LS7222 and a new 6-digit number can be entered.

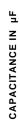

**KEYPAD INTERFACE** - The four X inputs and four Y outputs are designed for keypad interface (see Fig. 2). Since the X inputs have internal pull-ups, the maximum matrix size of 4 x 4 does not have to be utilized. Because the Y outputs have open drains, more than one LS7222 may share the same keypad.

During normal operation the LS7222 will scan the matrix looking for a switch closure. Once a closure has been detected, the internal key debounce logic determines if a "valid" key has been pressed or that if noise is just present. Only one valid input will be generated with any key closure. The use of internal key debouncing and Schmitt triggers on the inputs provides the LS7222 with very high noise immunity.

**TAMPER -** When a valid key has been detected by the LS7222, the entry is compared against the appropriate reference in the internal memory. If the requirements of digit value and code sequential position are not fulfilled, the Tamper output will momentarily go high; this indicates that an illegal code entry was attempted. The keypad entry enable timer and memory pointer will both be reset so that entry of the code can be attempted again.

| PIN         | FUNCTION       | TABLE 1. PIN DESCRIPTIONS<br>DESCRIPTION                                                        |  |  |  |  |

|-------------|----------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| 1           | Vss            | Supply voltage negative.                                                                        |  |  |  |  |

| 2           | RC-OSC         | Determines the LS7222's internal clock frequency, which is used for keyboard scanning           |  |  |  |  |

|             |                | and debounce. A resistor (to $VDD$ ) and a capacitor (to $Vss$ ) connected to this input sets   |  |  |  |  |

|             |                | the frequency.                                                                                  |  |  |  |  |

| 3, 4, 5, 6  | X1, X2, X3, X4 | The four X inputs and four Y outputs are designed to interface to a keypad matrix               |  |  |  |  |

| 7, 8, 9, 10 | Y1, Y2, Y3, Y4 | whose maximum allowable size is 4 by 4.                                                         |  |  |  |  |

| 11          | PROGRAM MODE   | This output goes high when the program mode is initiated. It resets to a low state after the    |  |  |  |  |

|             |                | 6-digit Arm/Disarm/Duress combination code has been programmed.                                 |  |  |  |  |

| 12          | CAP-M          | A capacitor connected between this input and Vss controls the duration of the Arm,              |  |  |  |  |

|             |                | Disarm and Tamper outputs.                                                                      |  |  |  |  |

| 13          | TAMPER         | Whenever a key is entered that is not a valid code element, this output goes high for a         |  |  |  |  |

|             |                | period determined by the capacitor on the CAP-M input.                                          |  |  |  |  |

| 14          | ARM            | This output generates an active high output every time the Arm code is entered,                 |  |  |  |  |

|             |                | irrespective of whether the circuit is currently in the disarm state or not. The duration of    |  |  |  |  |

|             |                | this output is determined by the capacitor on the CAP-M input. When the Arm and Disarm          |  |  |  |  |

|             |                | codes are identical, this output will occur on every other code entry.                          |  |  |  |  |

| 15          | ALARM          | When the Duress code is entered, this output latches high to enable an external alarm.          |  |  |  |  |

|             |                | The Alarm output resets to a low state when the Arm code is entered again.                      |  |  |  |  |

| 16          | DISARM         | This output generates an active high output every time the Disarm code is entered,              |  |  |  |  |

|             |                | irrespective of whether the circuit is currently in the armed state or not. The duration of     |  |  |  |  |

|             |                | this output is determined by the capacitor on the CAP-M input. When the Arm and Disarm          |  |  |  |  |

|             |                | codes are identical, this output will occur on every other code entry.                          |  |  |  |  |

| 17          | LOCK           | When the Disarm code or the Duress code is entered, this output latches high. When the          |  |  |  |  |

|             |                | Arm code is entered, the output latches low. If the Disarm or Duress code is entered            |  |  |  |  |

|             |                | when the output is already high (i.e. already disarmed), the output remains unaffected.         |  |  |  |  |

|             |                | Similarly, if the Arm code is entered when the output is already low (i.e. already armed), it   |  |  |  |  |

|             |                | remains unchanged. An exception to this rule is when the Arm and Disarm code identical          |  |  |  |  |

|             |                | in all 4 digits. In that situation, the output will toggle every time the code is entered.      |  |  |  |  |

| 18          | LOCK STATUS    | Functionally, this output is identical to the LOCK output, with the exception that its polarity |  |  |  |  |

|             |                | is reversed with respect to the LOCK output. This output is intended for driving a display      |  |  |  |  |

|             |                | lamp to indicate the lock status.                                                               |  |  |  |  |

| 19          | CAP-K          | A capacitor connected between this input and Vss sets the time limit for entering a 4 digit     |  |  |  |  |

|             |                | code from the keypad. (6 digits when initiating the program mode.)                              |  |  |  |  |

| 20          | Vdd            | Supply voltage positive.                                                                        |  |  |  |  |

| escent supply current: (100pF capacitor to Vss and 1<br>SYMBOL VDD |                              | M resistor to VDD, connected to the RC-OSC input) MAX UNIT                        |             |         |            |                      |  |

|--------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------|-------------|---------|------------|----------------------|--|

|                                                                    | 5V                           | 15                                                                                |             |         |            |                      |  |

| IDD                                                                | 9V                           | 25                                                                                | μA          |         |            |                      |  |

| IDD                                                                | 9V<br>12V                    | 25<br>30                                                                          | μΑ<br>μΑ    |         |            |                      |  |

| MAXIMUM RATINGS: (Volta                                            |                              |                                                                                   | <b>P</b>    |         |            |                      |  |

|                                                                    | -                            | -                                                                                 |             | UNIT    |            |                      |  |

| RATING                                                             | SYMBOL                       |                                                                                   | VALUE       |         |            |                      |  |

| DC supply voltage                                                  | Vdd                          |                                                                                   | 1 to +18    | V       |            |                      |  |

| Operating temperature range                                        | ТА                           | -25 to +70                                                                        |             | °C      |            |                      |  |

| Storage temperature                                                | TSTG                         | -65 to +150                                                                       |             | C°      |            |                      |  |

| DC Electrical Characteristics:                                     |                              |                                                                                   |             |         |            |                      |  |

| (Vss = 0V, VDD = +4V to +15V, =                                    | = 25°C TA +70°C unle         | ss otherwise                                                                      | specified)  |         |            |                      |  |

| PARAMETER                                                          | CONDITIONS                   | VDD                                                                               | MIN         | ТҮР     | MAX        | UNIT                 |  |

| Output source current                                              | Logic 1 Output               | 5V                                                                                | 1.50        | 2.50    | -          | mA                   |  |

| Lock Display, Arm, Disarm                                          | VOUT VDD - 2V                | 12V                                                                               | 5.60        | 8.25    | -          | mA                   |  |

| Alarm, Lock                                                        | VOOT VDD 2V                  | 15V                                                                               | 7.25        | 10.7    | _          | mA                   |  |

| Program Mode Outputs                                               |                              | 150                                                                               | 1.20        | 10.7    | -          | ША                   |  |

|                                                                    |                              |                                                                                   | 400         |         |            |                      |  |

| Output Sink Current                                                | Logic 0 Output               | 5V                                                                                | .400        | .60     | -          | mA                   |  |

| Lock Di <u>spla</u> y, Arm, Disarm                                 | VOUT Vss + 0.4V              | 12V                                                                               | 1.20        | 1.70    | -          | mA                   |  |

| Alarm, Lock<br>Program Mode Outputs                                |                              | 15V                                                                               | 1.50        | 2.25    | -          | mA                   |  |

| Output Source Current                                              | Logic 1 Output               | 5V                                                                                | .25         | .400    | -          | mA                   |  |

| Tamper Output                                                      | VOUT VDD - 2V                | 12V                                                                               | .20         | 1.30    | -          | mA                   |  |

|                                                                    | VOOT VDD-2V                  | 15V                                                                               | 1.10        | 1.70    | -          | mA                   |  |

| Output Sink Current                                                | Logic 0 Output               | 5V                                                                                | .060        | .100    | -          | mA                   |  |

| Tamper Output                                                      | VOUT Vss + 0.4V              | 12V                                                                               | .200        | .290    | -          | mA                   |  |

|                                                                    | VOUT V33 + 0. <del>4</del> V | 15V                                                                               | .250        | .370    | -          | mA                   |  |

| Input Level Detection                                              | Viн = Logic 1                | 5V                                                                                | 3.5         | -       | Vdd        | V                    |  |

| All Inputs                                                         | VIII = Eogle 1               | 12V                                                                               | 8.0         | -       | VDD        | V                    |  |

| All inputs                                                         |                              | 12V<br>15V                                                                        | 8.0<br>10.0 | -       | VDD<br>VDD | V                    |  |

|                                                                    |                              | 100                                                                               | 10.0        |         | VDD        | v                    |  |

|                                                                    | VIL = Logic 0                | 5V                                                                                | Vss         | -       | 1.6        | V                    |  |

|                                                                    | 0                            | 12V                                                                               | Vss         | -       | 4.0        | V                    |  |

|                                                                    |                              | 15V                                                                               | Vss         | -       | 5.0        | V                    |  |

|                                                                    |                              | 1                                                                                 |             |         |            |                      |  |

| FIGURE 3.                                                          |                              |                                                                                   | FIGURE 4.   |         |            |                      |  |

| KEYPAD ENTRY TIME vs.                                              |                              | LS7222 PULSE WIDTH ON ARM, DISARM AND TAMPER OUTPUTS vs. CAPACITOR ON CAP-M INPUT |             |         |            |                      |  |

| 5.0                                                                |                              | 10                                                                                | 5           |         |            | e4                   |  |

|                                                                    |                              |                                                                                   |             |         |            | 400 = 9 <sup>4</sup> |  |

|                                                                    |                              | _F                                                                                | ;           |         |            | 17                   |  |

| 4.0 —                                                              | ADS                          | 10 <sup>-6</sup>                                                                  | ~_          |         | /          |                      |  |

|                                                                    | FARU                         | 10                                                                                | 7           |         |            |                      |  |

| 3.0 - JOP 54                                                       |                              | 10                                                                                | -           |         |            | /                    |  |

| 2.0 - VDD 23V                                                      | NCE                          |                                                                                   | 3           | V00 12V |            |                      |  |

| 2.0                                                                |                              | 10                                                                                | 1           | NDD /   |            |                      |  |

|                                                                    | R<br>CAPACITANCE IN FARADS   | 10                                                                                | 9           | - /.8   | J. M. O    |                      |  |

| 1.0 - VDD = 1                                                      | 2V V                         | 10                                                                                |             |         |            |                      |  |

| NDU -                                                              |                              |                                                                                   |             | ///     |            |                      |  |

10<sup>-10</sup>

10<sup>-6</sup>

10<sup>-5</sup> 10<sup>-4</sup> 10<sup>-3</sup> 10<sup>-2</sup> PULSE WIDTH TIME IN SECONDS

10<sup>-1</sup>

10

1 2 3 4

0

V DD = 12V

5

7 8 9

6 ENTRY TIME IN SECONDS

### NOTES:

- 1. Keypad is typical 4 X 3 matrix type. Switch resistance should be 1k .

- **2**. Configuration shown is typical. The outputs of the LS7222 are functionally designed to provide either status or display information.

- 3. Resistors may be added in series with X inputs to provide protection against ESD from the keypad. R = 10k , 1/4 W.